此平台与产品1的区别在于,产品1的基带处理方案采用DSP(TMS320C6748)+FPGA(XC7K410T)方案,而产品2的基带处理为SOC方案,采用Xilinx的ZYNQ处理器(XC7Z100),片上集成双核ARM处理器(PS)以及丰富的逻辑可编程资源(PL),在单芯片上完成丰富的基带信号处理功能。因此下面重点看一下与产品1硬件方案上的区别,软件完成的接收机指标同产品1。

硬件实物参考图:

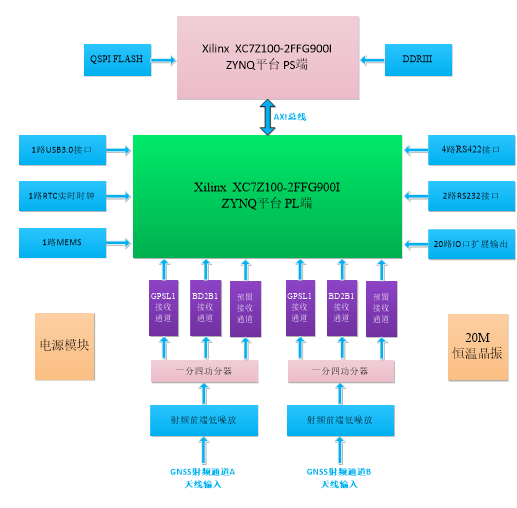

硬件原理结构框图:

主要硬件资源配置:

采用XILINX的Zynq7000 SOC 芯片XC7Z100-2FFG900I,该芯片采用ARM+FPGA SOC技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上,达到ARM处理和FPGA处理紧密配合,其双核ARM Cortex-A9 MPCore具有高性能,低功耗特性,双通道高速缓存,更高支持886MHz主频,另外拥有444K 个逻辑单元,26.5Mb片上存储器以及2020个乘法器资源;

FPGA的PS端外挂两片Micron(美光)的512MB的DDR3芯片,型号为MT41K256M16HA-125,两片DDR3 SDRAM组成32bit的总线宽度,做为程序加载后的运行存储器,PS端的DDR3 SDRAM的更高运行速度可达533MHz(数据速率1066Mbps);

FPGA的PS端外挂一片256MBit大小的Quad-SPI FLASH芯片,型号为W25Q256FVEI。由于QSPI FLASH的非易失特性,在使用中,它可以作为系统的启动设备来存储系统的启动镜像。这些镜像主要包括FPGA的bit文件、ARM的应用程序代码以及其它的用户数据文件;

FPGA的PL端外挂一片1路USB3.0接口芯片CYUSB3014,做为中频数据采集的高速上传接口传输到PC端。CYUSB3014是Cypress 公司出品的USB3.0 控制器,该款控制器集成了200MHz 的ARM9 控制器、512K 字节的RAM和USB 3.0物理层,具有可编程的100MHz GPIF II接口;

GPSL1/北斗二号B1射频接收芯片采用MAX2771, MAX2771为下一代全球导航卫星系统(GNSS)接收器,单芯片即可覆盖E5/L5、L2、E6、E1/L1波段,支持GPS、GLONASS、伽利略、QZSS、IRNSS和北斗导航卫星系统。MAX2771采用Maxim先进的低功耗SiGe BiCMOS工艺技术,能够以较低的成本提供更高性能和集成度。芯片上具有完整的接收链路,包括双路输入LNA和混频器,之后有滤波器、PGA和多位ADC,以及N分频频率合成器和晶振。该接收器的总噪声系数低至1.4dB。此外,MAX2771集成单芯片滤波器,完全不需要外部IF滤波器,仅需少量外部元件即可构建完整的低成本GNSS RF接收器方案。MAX2771是市场上最灵活的接收器。集成Δ-Σ N分频合成器可以在主机系统提供的任意参考频率或晶振频率下,以±30Hz (fXTAL = 32MHz时)的精度设置IF频率。ADC可以为I和Q通道输出1位或2位CMOS逻辑电平,或者为I通道输出高达3位CMOS电平。可将片上ADC旁路,模拟I和Q信号输出利用外部ADC进行采样。提供模拟监测特性,允许同时输出片上ADC采样和I模拟信号。

1路USB3.0接口芯片CYUSB3014,CYUSB3014是Cypress 公司出品的USB3.0 控制器,该款控制器集成了200MHz 的ARM9 控制器、512K 字节的RAM和USB 3.0物理层,具有可编程的100MHz GPIF II接口;

射频一分四表贴功分器Mini-WP4G+,频率范围1420~1660MHz,通道插损6.6dB,通道隔离度28dB;

射频前端低噪放采用Qorvo公司的SGL0622Z,它是一款低噪声SiGe HBT MMIC放大器,频率覆盖5MHz到4GHz范围;

板上参考时钟晶振:20MHz恒温晶振,0.01ppm;

板上提供高精度RTC实时时钟模块DS3234,在-40°C to +85°C温度范围内提供±3.5PPM 精度。

PL端外扩2路RS232串行接口,2路RS422差分串行接口;

注:如本产品提供的功能和指标与用户最终需求有差异的地方,可接受定制。